Allgemeines

- Projektordner herunterladen und entpacken

- Insgesamt gibt es 20 Punkte

- Die einzelnen Punkte bauen meist nicht aufeinander auf. Statt langer Fehlersuche lieber auf das nächste Beispiel wechseln.

Serielle Datenübertragung

Vorbereitung

- Projekt transmitter.xise öffnen

Aufgabenstellung

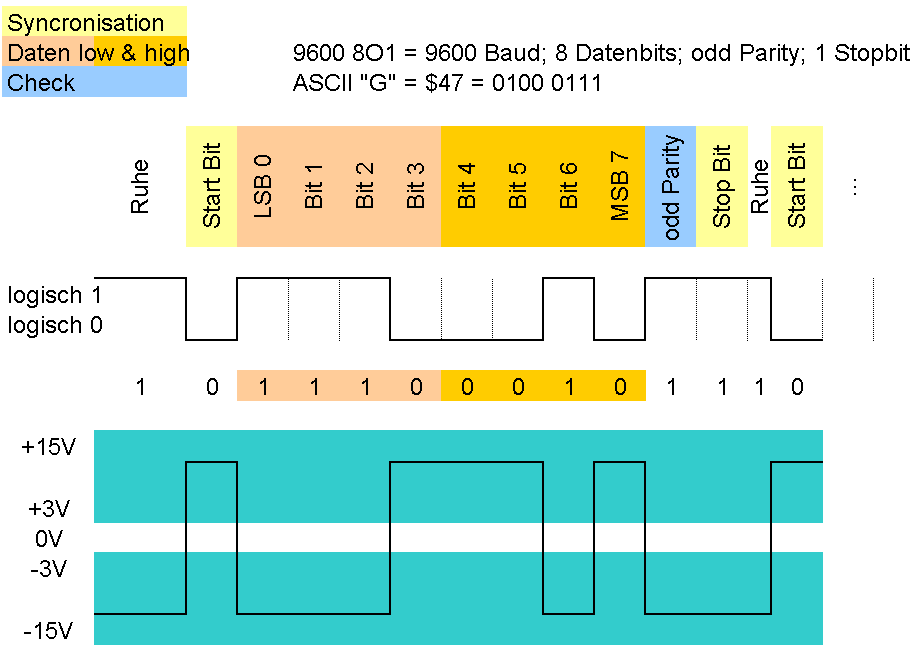

Um Daten zu übertragen wird oft die serielle Schnittstelle verwendet. In diesem Beispiel soll ein Transmitter entsprechend RS232 realisiert werden.

Zum Testen soll mittels der acht Umschaltern (SW0 bis SW7) ein 8 Bit Datenwort definiert werden und durch Drücken des Tasters BTN0 wird dieses dann versendet. Zum Versenden wird der Pegel der Sendeleitung mittels LED angezeigt. Die Baudrate wird auf 1 Baud gestellt.

uart_tx Komponente

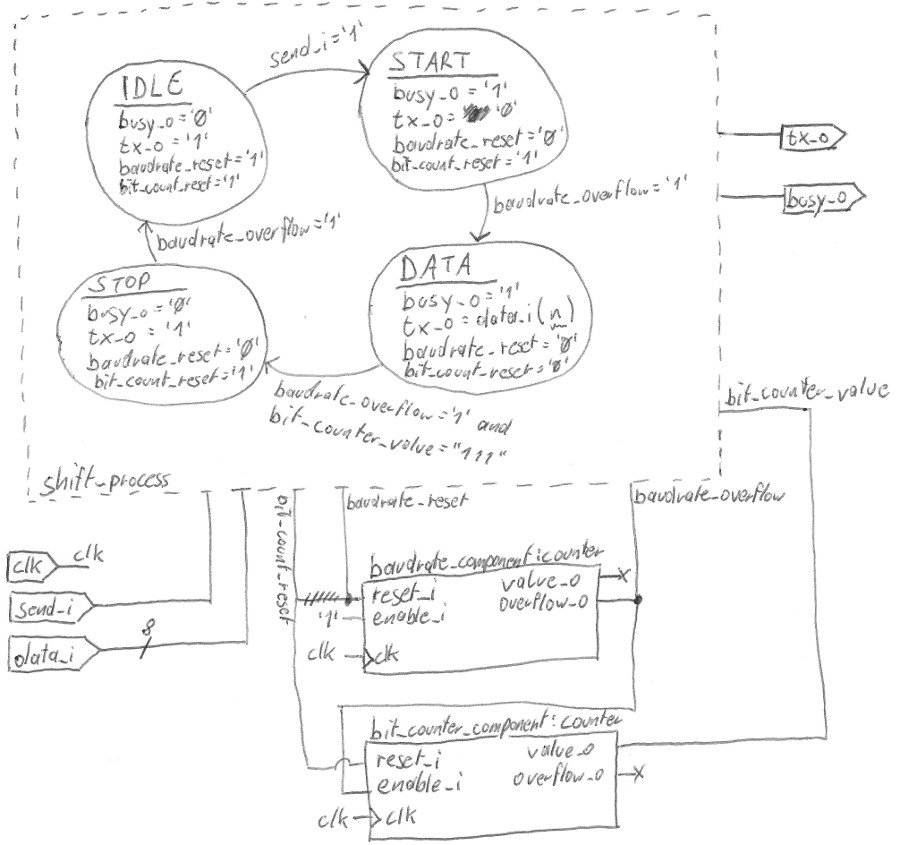

Zustandsmaschine

10 Punkte

- Die erforderliche Zustandsmaschine hat die Zustände

IDLE,START,DATAundSTOP - Eingänge:

send_i- startet die Übertragung- Überlauf den Baudraten Generators - wechselt bei einer laufenden Übertragung zum nächsten Symbol

- Ausgänge:

tx_o- das zu sendende Bit (bzw. Symbol)busy_o- zeigt eine laufende Übertragung an ('1'wenn eine Übertragung läuft)

- Wenn die Zustandsmaschine im Zustand

IDLEist undsend_igleich'1'ist, dann wird in den ZustandSTARTgewechselt. - Vom Zustand

STARTwird in den ZustandDATAgewechselt, sobald der Zähler für die Baudrate übergelaufen ist - Im Zustand

DATAläuft ein Bit Zähler und zählt die Bits von 0 bis 7 (LSB zuerst) - Jedes Bit wird für die Dauer ausgegeben, die sich aus der Baudrate ergibt

- Nach dem 8. Datenbit wird in den Zustand

STOPgewechselt - Vom Zustand

STOPwird in den ZustandIDLEgewechselt, sobald der Zähler für die Baudrate übergelaufen ist - Ausgabe von

tx_o- Ist in

IDLEundSTOPauf'1' - Ist in

STARTauf'0' - Entspricht während

DATAdem zu übertragenden Datenbit

- Ist in

Baudratengenerierung

2 Punkte

Für die Baudratengenerierung wird der bestehende Zähler (counter) verwendet. Die Entity enthält die beiden Generics BAUDRATE_WIDTH und BAUDRATE_DIVIDER, die den Zähler konfigurieren.

Bit Zähler

2 Punkte

Um die einzelnen Datenbits zu zählen (während des Zustands DATA) wird eine weitere Zählerinstanz verwendet. Diese Zählerinstanz zählt von 0 bis 7.

Der Ausgang value_o des Bit Zählers ist vom Typ std_ulogic_vector. Dieser muss zuerst in einen unsigned und dann mittels to_integer in einen Integer gewandelt werden, um mittels Indexzugriff das gewünschte Bit aus dem data_i Vektor zu holen (z.B. data_i(0) holt Bit 0 des Vektors).

Blockschaltbild

Dieses Blockschaltbild zeigt die einzelnen Komponenten der uart_tx Komponente. Die resultierende VHDL Beschreibung sollte äquivalent zu diesem Blockschaltbild sein.

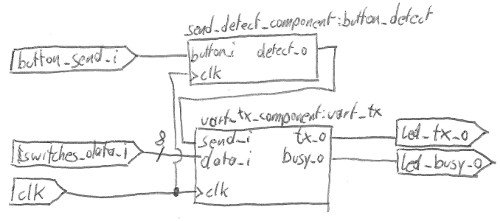

Implementierung des Top Levels

3 Punkte

Zur Verfügung stehen die Komponenten button_detect und uart_tx. Diese Komponenten werden genutzt, um im Top Level transmitter.vhd die gewünschte Funktionalität zu realisieren.

Einige benötigte Signale sind bereits vordefiniert.

Erstelle das Top Level anhand des folgenden Blockschaltbildes:

Erweiterung der Constraints Datei

2 Punkte

In der Datei transmitter.ucf ist nur das Signal clk definiert. Erweitere die Datei um folgende Zuordnungen

button_send_iliegt an PinG12switches_data_i(0)liegt an PinP11switches_data_i(1)liegt an PinL3switches_data_i(2)liegt an PinK3switches_data_i(3)liegt an PinB4switches_data_i(4)liegt an PinG3switches_data_i(5)liegt an PinF3switches_data_i(6)liegt an PinE2switches_data_i(7)liegt an PinN3led_tx_oliegt an PinM5led_busy_oliegt an PinM11

Test am Board

1 Punkt

Synthetisiere das Projekt und teste das Ergebnis am Board